ISO 3297:2007 Certified Vol. 4. Issue 8. August 2016

# Data Hinged Influential Reconfiguration of Surmised Arithmetic Entities for Video Encoding

Mohamed Yunus Parveez<sup>1</sup>, Dr. R. Shashi Kumar<sup>2</sup>

M.Tech (Digital Electronics), Department of Electronics and Communication, EWIT, Bengaluru, India 1 Professor, Department of Electronics and Communication, EWIT, Bengaluru, India<sup>2</sup>

**Abstract:** Low-power is a basic prerequisite for versatile media gadgets utilizing different sign handling calculations and structures. In most interactive media applications, the last yield is translated by human detects, which are not great. This blocks the need to deliver precisely remedy numerical yields. The field of surmised computing has gotten critical consideration from the research group in the previous couple of years, particularly with regards to different signal processing applications. Picture and video pressure calculations, for example, JPEG, MPEG, and various other formats are especially appealing contender for inferred figuring or surmised computing, since they are tolerant of registering imprecision because of human indistinctness, which can be misused to acknowledge exceedingly control productive especially in power efficient usage of these calculations. Be that as it may, existing surmised designs regularly settle the level of equipment estimation statically and are not versatile to information. For instance, if an altered induced equipment arrangement is utilized for a MPEG encoder in a fixed level of guess, the yield quality fluctuates extraordinarily for various info recordings. This paper addresses this issue by proposing a reconfigurable surmised construed design for MPEG encoders that advances power utilization with the objective of keeping up a specific Peak Signal-to-Noise Ratio (PSNR) edge for any video. In new design, we plan reconfigurable adder/subtractor segments (RABs), which can balance their level of guess, and subsequently coordinate these pieces in the movement estimation and discrete cosine change modules of the MPEG encoder. Note that in spite of the fact that the proposed reconfigurable surmised engineering is displayed for the particular instance of a MPEG encoder, it can be effectively reached out to other DSP applications.

**Keywords:** Surmised circuits, Surmised processing, Low power plan, Quality configurable, Scalable, Efficient.

# I. INTRODUCTION

utilization. The constrained view of human vision permits the yields of these calculations to be numerically surmised instead of precise. This unwinding on numerical precision gives some flexibility to complete loose or surmised calculation. The opportunity can be exploited to think of low-power outlines at various steps of configuration deliberation, viz. rationale, design, and calculation.

Presenting a restricted measure of registering imprecision in picture and video preparing calculations frequently that a little unwinding in yield accuracy can bring about enhancement strategies. significantly less complex and lesser power usage. In any experience the ill effects of the constraint that, for broadly give a quality bound on the output, and now and again, the of the transistors in a mirror adder. An imperative point to

Normally utilized mixed media applications have Digital Output quality might be seriously degraded. The principle Signal Processing (DSP) hinders as their spine. A huge explanation behind this yield quality fluctuation is that the portion of these digital signal processing blocks actualize Degree of Approximation (DA) in the equipment picture and motion images handling calculations, where a engineering is fixed statically and can't be tweaked for definitive yield is either a picture or a video for human various inputs. There has been a considerable measure of exertion in developing vitality productive video pressure plans. A hefty portion of them are identified with the particular instance of a MPEG encoder. Diverse strategies for electrical power reduction incorporate algorithmic alterations, voltage over-scaling and uncertain calculation of measurements. By starting of surmised calculative procedures has opened up completely new open doors in building low-power video pressure structures. Surmised processing strategies accomplish a lot of voltage and current saving by presenting a little measure of mistake or brings about an immaterial measure of noticeable visual error into the rationale part. Diverse methodologies for change in the yield, which makes these calculations as estimation incorporate error presentation through voltage perfect possibility for the utilization of surmised figuring over-scaling, intelligent rationale control and circuit structures. Surmised processing designs exploit the way rearrangements and reduction utilizing don't care based

case, most surmised hardware designs proposed so far The techniques in past procedures present imprecision by supplanting adders with their surmised partners. The Changing info parameters, it turns out to be difficult to surmised adders are gotten by brilliantly erasing a portion

ISO 3297:2007 Certified

Vol. 4, Issue 8, August 2016

There additionally exist occasions of approximations presented in a MPEG encoder. A large portion of them adventure the inalienable mistake strength of the motion estimation (ME) calculation, which results in minor quality debasement.

For instance, Moshnyaga utilize a bit-width pressure method to lessen power utilization of video edge memory. Moshnyaga, Liou and He et al. use bit truncation to present approximations in the ME segment of a MPEG encoder. A versatile piece veiling strategy is proposed, where the creators propose to truncate the pixels of the present and past frames required for ME relying on the quantization step. In any case, such a coarse-grained information truncation is relevant just to the particular instance of ME and gives inadmissible results for different segments, for example, discrete cosine transform (DCT), which requires a better direction over mistake.

As if there should arise an occurrence of beforehand proposed papers, this paper additionally points in approximating or surmising the adders of the ME and DCT segments of a MPEG encoder. In any case, this paper presents the idea of influentially reconfigurable approximation, which, I will allude, helping in keeping up better control over application-level quality measurements while at the same time profiting in lesser power consumption from hardware approximation. Likewise, such element reconfiguration additionally furnishes clients with a control handle for differing the yield nature of the recordings and the power utilization for the battery-fueled sight and sound gadgets.

This paper incorporates some of extra elements as depicted here. We increase the heuristics for adjusting the DA of the reconfigurable equipment obstructs by including the element of most huge piece (MSB) truncation, which enhances the vitality quality trade-off amid the video encoding process. We likewise extend the RAB to incorporate three extra viper structures, viz., CLA, CBA, and CSA. Likewise, for the carry lookahead hinged RAB, we propose dual mode carry lookahead and propagate generator segments or engender create obstructs as its constituent essential building pieces. At last, we give a similar investigation of the power utilization of the distinctive RABs furthermore exhibit how the DA is consequently controlled crosswise over various edges amid run-time.

#### II. RELATED WORK

Influential variety of the DA should be possible when each of the adder/subtractor segments is outfitted with one or a greater amount of its surmised duplicates and it can switch prerequisite. them between according to refers various types of surmised circuits for adders. In any that they induce as Approximation Don't Cares (ADCs)

note is that these surmised circuits are hardwired and can't case, it likewise should be guaranteed that the extra range be changed without resynthesizing the whole circuit. overheads required for developing the reconfigurable surmised circuits are minimal with sufficiently large power savings. Their methodology intends to disentangle the multifaceted nature of a routine mirror adder cell by decreasing the quantity of transistors furthermore the load capacitance. At the point when the mistakes presented by these approximations are reflected at an abnormal state in a commonplace DSP calculation, the effect on yield quality is practically unimportant. A lessening in the compelling exchanged capacitance results in a lower power scattering. In addition, the proposed approximate FA cells additionally permit the framework to work at a lower supply voltage than the customary case. This further adds to a quadratic lessening in force dissemination. An additional advantage because of lower number of transistors is a lessening in absolute region. While procedures like SDC and ANT have a territory overhead, despite what might be expected, our method gives considerable range reserve funds as well. They have exhibited the utility of the proposed surmised FA cells in two DSP frameworks, viz. picture and video pressure. They trust that they can be utilized on the highest point of officially existing low-control systems like SDC and ANT to separate multifold advantages with an extremely negligible misfortune in yield quality [1].

> They additionally determined disentangled numerical models for blunder and power utilization of an estimated RCA utilizing the rough FA cells. Utilizing these models, we talked about how to apply these approximations to accomplish most extreme force funds subject to a given quality requirement. This method has been represented for two illustrations, DCT and FIR channel. We trust that the proposed surmised adders can be utilized on top of effectively existing low-control procedures like SDC and ANT to remove extra advantages with a maximal negligible misfortune in yield quality [2]. Another plan has been displayed for lessening vitality utilization of video (or edge) memory. Specifically, we focused on the decrease of the quantity of moves happening on the bitlines. Recreations of the proposed procedure utilizing an assortment of video signs have demonstrated that our methodology can spare as much as 21% of vitality devoured by the edge memory cell exhibit in contrast with the full determination memory access, without influencing the photo quality and throughput. The plan disposes of pointless sign moves which occur in the most critical bits of pixel because of sign augmentation by modifying powerfully the bit-width to the pixel variety [3]. Workmanship information here, going from surmised circuit outline, estimated design investigation to rough programming usage. At long last, we highlight some open difficulties for future work in this area [4].

This With a specific end goal to accomplish these Advantages reconfigurable engineering can incorporate any surmised SALSA encodes the quality limitations utilizing rationale variant of the adders/subtractors. The scheduled paper capacities called Q-capacities, and catches the exibility

ISO 3297:2007 Certified Vol. 4. Issue 8. August 2016

which are utilized for circuit improvement utilizing conventional couldn't care less based streamlining methods, consequently incorporate rough circuits going from number arithmetic building segments such as adders, multipliers, MAC to whole information ways such as DCT, FIR, IIR, SAD, FFT Buttery, Euclidean separation, exhibiting versatility and noteworthy enhancements in territory 1.1X to 1.85X for tight mistake requirements, and 1.2X to 4.75X for loose blunder limitations and power from 1.15X to 1.75X for tight mistake imperatives, and 1.3X to 5.25X for loose blunder imperatives[5]. Besides, the calculation is controlled by an entropy rule with the goal that it accomplishes an ideal data transfer capacity allotment between the DFD data and the movement parameters. Recreation results have demonstrated that the technique results in an enormously upgraded visual nature of the reproduced grouping and a noteworthy sparing as far as bit rate. The reproduction results and diagnostic figuring's demonstrate that an impressive number of correlation exist in the structures talked about, and our improvement succeeded in dispensing with just about fifty percent [6] [7]. Dissect the impact of ME blunders because of DVS in general coding execution and also they propose a model for the subsequent rate increment at a given altered quantization parameter as a component of info qualities and information voltage, for given ME calculation and MMC engineering. This model is accepted utilizing re-enactment's [8]. Power productive movement estimation (ME) utilizing various uncertain aggregate total contrast (SAD) metric computations. We amplify late work in up and coming exploration by giving scientific arrangements in light of demonstrating of calculation blunders because of voltage over scaling (VOS) and subexamining (SS) [9]. Re-enactment results show normal power savings of ~ 33% for the proposed engineering when contrasted with traditional execution in the 90 nm CMOS innovation. The greatest yield quality misfortune regarding Peak Signal to Noise Ratio (PSNR) was ~ 1 dB without acquiring any throughput punishment [10]. probabilistic math can be utilized to figure the Fast Fourier Transform in an amazingly vitality productive way, yielding vitality funds of more than 5.6X with regards to the broadly utilized engineered opening radar SAR application[11].

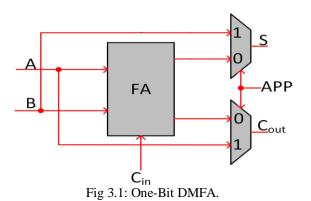

The utilization of influentially reconfigurable surmised hardware structures that change the DA amid run-time over different execution cycles, contingent upon the data input. Toward this end, we propose the configuration of in order to construct the proposed architecture it require reconfigurable adder/subtractor segments (RABs) for four the following components. normally utilized adder structures, viz., ripple carry adders (RCA), carry lookahead adders (CLA), carry bypass adder 3.1 ONE-BIT DMFA BLOCK predetermined bound.

### III.DESIGN METHODOLOGY AND PROPOSED **ARICHETECTURE**

Influential variety of the Degree of approximation should be possible when each of the adder/subtractor segments is outfitted with one or a greater amount of its surmised duplicates and it can switch between them according to necessity. This reconfigurable engineering can incorporate any surmised form of the adders/subtractors. As a source of perspective to the past papers they proposed six various types of surmised circuits for adders. Nonetheless, it likewise should be guaranteed that the extra region overheads required for developing the reconfigurable surmised circuits are insignificant with adequately expansive power savings. In the proposed design method, for a settled level of hardware approximation in a MPEG encoder, the yield quality shifts generally crosswise over various recordings, regularly going underneath adequate breaking points.

This demonstrates setting the level of equipment estimation statically is inadequate. So thought of researching, surprisingly, the utilization of influentially reconfigurable surmised hardware designs that shift the DA amid run-time over different computational cycles, contingent upon the inputs. Toward this end, Research proposes the configuration of reconfigurable adder/subtractor hinders for four regularly utilized adder designs, viz., ripple carry adder, carry look-ahead adder, carry bypass adder, and carry select adder, in order to achieve data hinged influential reconfiguration on video encoders using surmised arithmetic units and in this way coordinate them into the MPEG encoder to empower quality configurable execution.

This is impractical for altered equipment, and accordingly a need emerges for reconfiguring the engineering in light of the qualities of the video being seen. As cases, we have picked the two most guileless techniques displayed in the refered papers, to be specific, truncation and guess, for approximating the adder/subtractor pieces. The last one can likewise be conceptualized as an upgraded adaptation of truncation as it just transfers the two 1-bit inputs, one as Sum and alternate as Carry Out. On the off chance that A, B, and Cin are the 1-bit inputs to the full adder (FA), then the yields are Sum = B and Cout = A. The resultant truthtable demonstrates that the yields are right for more than half of all information mixes, along these lines ended up being a superior estimation mode than truncation. Hence

(CBA), and carry select adder (CSA), and along these It is surely understood that as the adders are normally lines incorporate them into the MPEG encoder to intended for the most pessimistic scenario where their empower quality configurable execution. Here the article helps engender through the whole bits but those cases proposes an outline procedure to adjust the DA seldom happen at genuine operation. So in order to influentially taking into account the video attributes with achieve real world work this research exploits the rare the objective of guaranteeing that yield quality is inside a most pessimistic scenario events by outlining adders for the normal case as opposed to the most pessimistic

ISO 3297:2007 Certified

Vol. 4, Issue 8, August 2016

scenario ,Normal case outline infers that calculation yields 0 regardless of the info. Demonstrates the rationale exhibited, empowering to locate the ideal outline point. I creating the suitable select signs for the multiplexers. this event we demonstrate that for situations where the framework's basic ways are managed by the adders, the A multimode FA cell would give even a superior framework's operation voltage can be diminished by their cautious outline, without hurting the clock cycle and with little execution debasement. Potential vitality investment funds of up to half is appeared. Double mode expansion can likewise be extremely valuable in exceptional models, for example, picture processors, where profound pipeline of increments is required for weighted pixel shading averaging. It is intriguing to ponder the ramifications of the augmented mode likelihood on the vitality and execution.

The present plan replaces every Full Adder cell of the adders/subtractors with a double mode or Dual Mode Full Adder (DMFA) block in which every Full Adder cell can work either in completely precise or in some estimation mode relying upon the condition of the control signal APP. A rationale high estimation of the APP signal signifies that the DMFA is working in the surmised mode.It represents these adders/subtractors as RABs. Our trials have demonstrated unimportant distinction in the force utilization of DMFA when worked in both of the two guess modes. Subsequently, with no loss of consensus, estimate was decided for its higher likelihood of giving the right yield result than truncation, which constantly yields 0 independent of the info.

Note that the FA cell is power gated when working in the surmised mode. Amalgamation and assessment of power utilization of a 16-bit RCA were worked in Synopsys Design and Power Compiler and the relating results are depicted. Our analyses have demonstrated a unimportant distinction in the power utilization of DMFA when worked in both of the two guess modes.

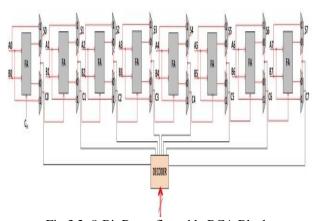

## 3.2 8-BIT RECONFIGURABLE RCA BLOCK

Subsequently, with no loss of sweeping statement, estimate 5 was decided for its higher likelihood of giving S=P^Cin, Cout = G+PCin. the right yield result than truncation, which perpetually The surmised mode includes P=B, G=A, S=B, Cout = A.

blunders may happen. Those are being amended by piece chart of the DMFA cell, which replaces the actualizing a double expansion mode with the guide of a constituent FA cells of an 8-bit RCA, what's more, it committed control circuit. A force delay-vitality model is additionally comprises of the estimate controller for

> contrasting option to the DMFA from the purpose of controlling the guess extent. Be that as it may, it likewise builds the unpredictability of the decoder piece utilized for attesting the privilege select signs to the multiplexers and the rationale overhead for the multiplexers themselves. This undermines the essential goal as the vast majority of the force reserve funds that we get from approximating the bits are lost. Rather, the two-mode decoder and the 2:1 multiplexers have immaterial overhead furthermore give adequate command over the guess degree.

Fig 3.2: 8-Bit Reconfigurable RCA Block.

#### 3.3 CARRY PROPAGATE GENERATE BLOCKS

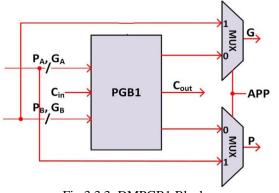

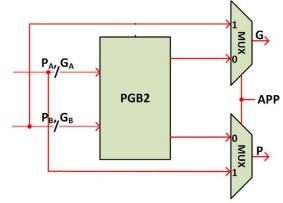

The essential segments present at the more elevated amounts of CLA chain of command are signified as engender and generate segments, PGB1 and PGB2. For this situation, PGB1 produces an additional Cout yield as contrasted and PGB2. The configurable double mode renditions DMPGB1 and DMPGB2 use data in as PA and GB as surmised for yields P and G, individually, when working in the surmised mode.

These surmised values were chosen observationally guaranteeing that the proportion of the likelihood of right their relating double mode variants, DMCLB1 and DMCLB2, have both S and P surmised by information operand B and both Cout and G approximated by info operand A.

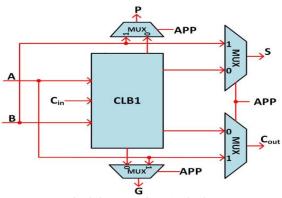

#### 3.3.1 DMCLB1

The Dual Mode CLB1 Block Consist CLB, Four Multiplexers. These are used to create four yield like S, C, P, G. it depends on guess and Accurate mode.

DMCLB1design Accurate mode P, G, S, Cout Values comprise of these Four Equations. P=A^B, G=A&B,

ISO 3297:2007 Certified

Vol. 4, Issue 8, August 2016

Fig 3.3.1: DMCLB1 Block.

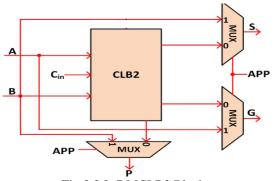

#### 3.3.2 DMCLB2

The Dual Mode CLB2 Block Consist CLB, Three Multiplexers. It's utilized to produce three yields like G, S, C, and P; it depends on guess and accurate mode. DMCLB2design Accurate mode P, G, S, Cout Values comprise of these Three Equations. P=A^B, G=A&B, S=P^Cin. The surmised mode includes P=B,G=A, S=B.

Fig 3.3.2: DMCLB2 Block.

#### 3.3.3 DMPGB1

The Dual Mode PGB1 segment Consist PGB, Two Multiplexers. It's utilized to produce three yields like G, C, and P; it depends on surmised and accurate mode. DMPGB1design Accurate mode P, G, S, Cout Values comprise of these three Equations. P=P\_A^P\_B, G=G\_B+G\_A&G\_B, Cout=G+(P&Cin). The surmised mode consists of: P=P\_A, G=G\_B, Cout = G+PCin.

Fig 3.3.3: DMPGB1 Block.

#### 3.3.4 DMPGB2

The Dual Mode PGB2 segment Consist PGB, Two Multiplexers. It's utilized to produce three yields like G, C, and P; it depends on surmised and accurate mode. DMPGB1design Accurate mode P, G, S, Cout Values comprise of these two Equations:  $P=P_A^P_B$ ,  $G=G_B+G_A\&G_B$ . The surmised Mode Consist of Four: Values  $P=P_A,G=G_B$ .

Fig 3.3.4: DMPGB2 Block.

The force gating transistor and the multiplexers of the DMFA are intended to acquire the minimum conceivable overhead. Our trials demonstrate that exchanging of the CMOS transistors contributes toward the greater part of the aggregate force utilization of the FA and DMFA squares. Table I exhibits the force utilization of FA and DMFA for various modes acquired by thorough reproduction in modalism and Xilinx device. It demonstrates that the force increments by 0.21 µW when we work DMFA in precise mode as contrasted and the first FA segment. This distinction in force can be credited predominantly to the expansion in burden capacitance of the FA hinder because of the expansion of the info capacitance of the interfaced multiplexers. A little divide of the aggregate force is contributed by the extra exchanging of the multiplexers. The results likewise demonstrates that the power expended amid DMFA estimated mode is verging on insignificant when contrasted and the precise mode, which is because of the force gating of the FA hinder by the pMOS transistor, as appeared DMFA.

Diminishment in the info exchanging action of the multiplexers is additionally an auxiliary reason for this little measure of power. The extra overhead because of exchanging of the power gating transistor can be ignored, since its exchanging action is little because of the way of our exchanging calculations. This is primarily due to the spatial and fleeting territory of the pixel values crosswise over successive edges. The idea of RAB can likewise be stretched out to other adder designs also adder models, for example CBA and CSA which likewise contain FA as the central building segment can be made exactness configurable by direct substitution of the FAs with DMFAs.

ISO 3297:2007 Certified

Vol. 4, Issue 8, August 2016

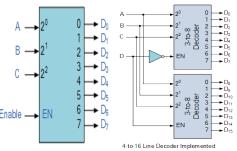

#### 3.4 DECODER

consisting input of 2-bit, 3-bit or 4-bit codes relying on the quantity of information lines, Hence a decoder that consist of an arrangement either 2 or more bits will be characterized as having a n-bit code, and in this manner it is shifted. will be conceivable to speak to 2n conceivable qualities. Accordingly, a decoder for the most part disentangles a binary esteem into a non-double one by setting precisely one of its n yields to rationale "1". So for instance, the decoder having 3 paired inputs n = 3, would create a 3 to 8 line decoder and 4 data info would deliver a 4-to-16 line decoder et cetera.

Fig 3.4: Decoder Block Diagram Decoder, Implemented with two 3-to-8 Decoder.

Inputs A, B, C are utilized to choose which yield on either decoder will be at rationale "1" and information D is utilized with the empower contribution to choose which encoder either the first or second will yield the "1". Nonetheless, there is an utmost to the quantity of inputs that can be utilized for one specific decoder, in light of the fact that as n expands, the quantity of AND gates required to deliver a yield likewise gets to be bigger bringing about the fan-out of the gates used to drive them turning out to be huge.

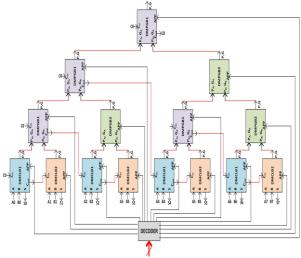

### 3.5 8-BIT RECONFIGURABLE CLA BLOCK

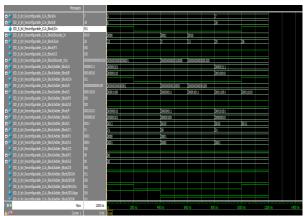

Different assortments, as CLA and tree adders, use diverse sorts of carry engender and produce carry generate as their essential building units, and subsequently require some extra changes to work as RABs. For instance, we actualized a 16-bit CLA comprising of four distinct sorts of fundamental blocks contingent on the nearness of entirety or sum (S), Cout, convey proliferation or carry propagation (P), and convey era or carry generation (G) at various levels, here the main point is to address the fundamental segments present at the first or least significant bit level of a CLA, which have inputs coming in specifically, as carry lookahead segments CLB1 and CLB2. The distinction among them being that CLB1 produces an extra Cout signal contrasted and CLB2. Their comparing double mode or dual mode adaptations, DMCLB1 and DMCLB2, have both S and P surmised by information operand B and both Cout and G surmised by data operand A, as appeared in figure 3.5. Hence the experimental results and the DMFA blocks which produces the sequential values demonstrate a similar

investigation of the power utilization of the distinctive Binary Decoders are one sort of Digital Logic gadget sorts of adders when the degree of approximation from the full point is shifted. Specifically, the diagrams and the designs signify the standardized power utilization of the diverse sorts of RABs when the quantity of bits surmised

Fig 3.5: 8-Bit Reconfigurable CLA Block.

A fascinating perception for CSA is that estimating its most significant bit gives more noteworthy power savings reserve than least significant bit estimate per bit. This can be credited to the design of the carry save adders, where surmising every bit in the most significant bit results in power gating of two FAs contrasted and one FA when the LSBs are surmised. The graphs additionally delineate that genuine force investment funds are started when the DA is equivalent to or above 5. Here it refers to savings do to surmised because of estimate surpasses the overhead brought about because of the extra multiplexers, power gating transistors, and controller. The inborn mistake versatility appeared by the ME and the little inputs to the DCT square give adequate chances to accomplishing a high DA much more prominent than 5 and in this way high power investment funds.

## IV.RESULTS AND ANALYSIS

#### 4.1 Simulation Outputs

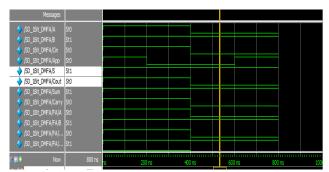

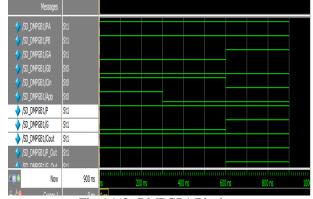

Fig 4.1(a): 1-Bit DMFA

ISO 3297:2007 Certified

Vol. 4, Issue 8, August 2016

The snapshot shows a aftereffect of 1-Bit DMFA with 3 Synthesis and evaluation of power consumption of a 8-bit inputs i.e. A, B, Cin to the Full Adder and another ascribe RCA were performed using Xilinx.SE 9.1 version and APP i.e. selection line either for selection of MUX1 or MUX2 in which each Full adder corpuscle can accomplish either in absolutely authentic or in some surmised mode depending on the accompaniment of the ascendancy signal APP. A logic high value of the APP signal denotes that the DMFA is operating in the surmised mode. Outputs also have a wire connection of sum and carry. It is simulated result of 1-bit DMFA obtained from Modalism Firmware by creating a separate files for each execution. Initially for the creation of module, Here the main requirement is of input or data values for the respective cells or blocks which we are using in respective module the in order to get the output we have to select the APP either at logic 1 or 0 then after completion of program part next is to perform compilation of the module and then simulate. Hence the achievement can be apparent in the anatomy of waveform with corresponding constraints.

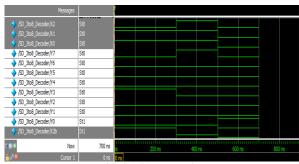

Fig 4.1(b): Decoder

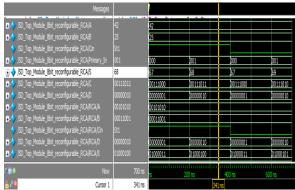

Fig 4.1(c): Top Module 8-Bit Reconfigurable RCA Block

The result of 8-Bit RCA consist of 8 different DMFA blocks, now it consists of 32 inputs and 16 outputs in which the carry is connected in such a way that it forms as a ripple carry adder hence outputs (carry) of reconfigurable adder/subtractor blocks are now connected project, select new program file in xilinx and write required code and simulate then give the inputs which got 67 in surmised mode and in the accurate we got 68. at high speed, which consist of gross of 29 I/Os.

Modelsim 6.4 .a version. RCA also consists of Approximation controller for generating the appropriate select signals for the multiplexers.

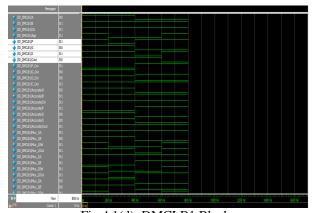

Fig 4.1(d): DMCLB1 Block.

Fig 41(e): DMCLB2 Block.

Fig 4.1(f): DMPGB1 Block.

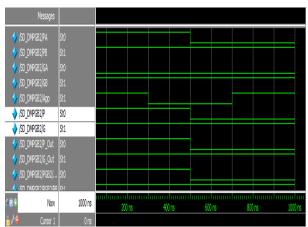

to the decoder to form 8-bit RCA. Now create a new Result analysis regarding the main 8-bit reconfigurable CLA design ,first of all the proposed architecture consist of DMCLB1,DMCLB2,DMPGB1,DMPGB2, 16 BIT have to be tested then select a run button, then the required DECODER. Now create a new file regarding above results are obtained here we had manually for one input mentioned block and it is considered as the top most we gave 10 and for another we gave 53 here in output we output file which has an output format of NGC, operating

# **IJIREEICE**

# International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

ISO 3297:2007 Certified Vol. 4, Issue 8, August 2016

Fig 4.1(g): DMPGB2 Block.

Fig 4.1(h): Main 8-Bit Reconfigurable CLA Block

It uses 29 I/O buffers in which 21 are inputs and 8 are outputs. As the proposed model is designed for reduction of both power and path delay, the maximum combinational path delay found is 15.519ns (9.220ns logic, 6.299ns route) its utilized 136 paths and 8 destination ports. Power output is reduced drastically from 42mW to 28mW.

#### 4.2 Synthesis Report

| Device Utilization Summary                     |       |           |             |         |  |  |

|------------------------------------------------|-------|-----------|-------------|---------|--|--|

| Logic Utilization                              | Used  | Available | Utilization | Note(s) |  |  |

| Number of 4 input LUTs                         | 16    | 3,840     | 1%          |         |  |  |

| Logic Distribution                             |       |           |             |         |  |  |

| Number of occupied Slices                      | 10    | 1,920     | 1%          |         |  |  |

| Number of Slices containing only related logic | 10    | 10        | 100%        |         |  |  |

| Number of Slices containing unrelated logic    | 0     | 10        | 0%          |         |  |  |

| Total Number of 4 input LUTs                   | 16    | 3,840     | 1%          |         |  |  |

| Number of bonded IOBs                          | 25    | 97        | 25%         |         |  |  |

| Total equivalent gate count for design         | 105   |           |             |         |  |  |

| Additional JTAG gate count for IOBs            | 1,200 |           |             |         |  |  |

Fig 4.2(a): Device Utilization Summary for 8-Bit Normal CLA.

| Device Utilization Summary                     |       |           |             |         |  |  |

|------------------------------------------------|-------|-----------|-------------|---------|--|--|

| Logic Utilization                              | Used  | Available | Utilization | Note(s) |  |  |

| Number of 4 input LUTs                         | 26    | 3,840     | 1%          |         |  |  |

| Logic Distribution                             |       |           |             |         |  |  |

| Number of occupied Slices                      | 15    | 1,920     | 1%          |         |  |  |

| Number of Slices containing only related logic | 15    | 15        | 100%        |         |  |  |

| Number of Slices containing unrelated logic    | 0     | 15        | 0%          |         |  |  |

| Total Number of 4 input LUTs                   | 26    | 3,840     | 1%          |         |  |  |

| Number of bonded IOBs                          | 29    | 97        | 29%         |         |  |  |

| Total equivalent gate count for design         | 156   |           |             |         |  |  |

| Additional JTAG gate count for IOBs            | 1,392 |           |             |         |  |  |

Fig 4.2(b): Device Utilization Summary for 8-Bit Reconfigurable CLA.

| Power summary:                     | I(mA) | P(mW) |  |

|------------------------------------|-------|-------|--|

| Total estimated power consumption: |       | 42    |  |

|                                    |       |       |  |

| Vccint 1.20V:                      | 10    | 12    |  |

| Vccaux 2.50V:                      | 10    | 25    |  |

| Vcco25 2.50V:                      | 2     | 5     |  |

|                                    |       |       |  |

| Inputs:                            | 0     | 0     |  |

| Logic:                             | 0     | 0     |  |

| Outputs:                           |       |       |  |

| Vcco25                             | 2     | 5     |  |

| Signals:                           | 0     | 0     |  |

|                                    |       |       |  |

| Quiescent Vccint 1.20V:            | 10    | 12    |  |

| Quiescent Vccaux 2.50V:            | 10    | 25    |  |

Fig 4.2(c): Power Consumption Summary for 8-Bit Normal CLA.

| Power summary:                     | I(mA) | P(mW) |  |

|------------------------------------|-------|-------|--|

| Total estimated power consumption: |       | 38    |  |

|                                    |       |       |  |

| Vccint 1.20V:                      | 10    | 12    |  |

| Vccaux 2.50V:                      | 10    | 25    |  |

| Vcco25 2.50V:                      | 0     | 1     |  |

|                                    |       |       |  |

| Inputs:                            | 0     | 0     |  |

| Logic:                             | 0     | 0     |  |

| Outputs:                           |       |       |  |

| Vcco25                             | 0     | l     |  |

| Signals:                           | 0     | 0     |  |

|                                    |       |       |  |

| Quiescent Vccint 1.20V:            | 10    | 12    |  |

| Quiescent Vccaux 2.50V:            | 10    | 25    |  |

Fig 4.2(d): Power Consumption Summary for 8-Bit Reconfigurable CLA.

### 4.2.1 Area, Delay and Power Comparison

The main purpose of designing the proposed architecture is for power saving, reduction in both delay and area. Hence the comparison of these parameters are shown in table 4.1.

ISO 3297:2007 Certified

Vol. 4, Issue 8, August 2016

Table4.1: Area, Delay and Power.

| Method                            | Area |        |            | Delay    |             |             | Power |

|-----------------------------------|------|--------|------------|----------|-------------|-------------|-------|

|                                   | LUT  | Slices | Flip Flops | Delay    | Logic Delay | Route Delay | (mW)  |

| Normal CLA                        | 16   | 10     | 105        | 17.423ns | 10.201ns    | 7.221ns     | 42    |

| Proposed<br>Reconfigurable<br>CLA | 26   | 15     | 156        | 15.519ns | 9.220ns     | 6.299ns     | 28    |

#### V. CONCLUSION

From the proposed work, System comprises of a reconfigurable surmised engineering for the MPEG encoders that advance power utilization while keeping up yield quality crosswise over various info recordings. The proposed engineering depends on the idea of influentially or progressively reconfiguring the level of estimation in the hardware taking into account the info attributes. It requires the client to indicate just the general least quality for recordings as opposed to deciding the level of equipment --approximation. The trial results demonstrate that the proposed engineering results in power saving proportionate to a benchmark approach that utilizations altered surmised hardware while regarding quality imperatives crosswise over various recordings. Future work incorporates the consolidation of other surmised procedures and extending the approximations to other number-crunching and utilitarian segments which could be useful in building furthermore reaching out to other DSP applications.

#### REFERENCES

- [1] Vaibhav Gupta, Anand Raghunathan, Debabrata Mohapatra, Sang Phill Park and Kaushik Roy, "IMPACT: Imprecise adders for lowpower Approximate Computing", in Proc. 17th IEEE/ACM Int. Symp. Low-Power Electron.Design (ISLPED), Aug. 2011.

- [2] Anand Raghunathan, Debabrata Mohapatra, Kaushik Roy and Vibhav Gupta, "Low-Power Digital Signal Processing Using Approximate Adders", IEEE Trans Computer Aided Design Integrated Circuits Systems., vol. 32, no. 1, pp. 124–137, Jan. 2013.

- [3] Koji Inoe, Mizuka Fukagawa and Vasily G. Moshnyaga, "Reducing Energy Consumption of Video Memory by Bit Width Compression", in Proc. Int. Symp. Low Power Electron. Design (ISLPED), 2002, pp. 142–147.

- [4] Qiang Xu, Tood Mytkowiz and Name Sung Kim, "Approximate Computing: A Survey" IEEE Trans Design and Test., proposed in 2015.

- [5] Vivek Kozhikkottu, Kaushik Roy, Amit Sabne, S. Venkataramani, "SALSA: Systematic Logic Synthesis of Approximate Circuits", in Proc. 49th Annu. Design Autom. Conf. (DAC), Jun. 2012, pp. 796– 801.

- [6] Frederic Dufaux and Fabrice Moscheni, "Motion Estimation Techniques for Digital TV: A Review and A New Contribution", Proc. IEEE, vol. 83, no. 6, pp. 858–876, Jun. 1995.

- [7] Mohamed A. Elgamel, Ahmed M. Shams and Magdy A. Bayoumi, "A Comparative Analysis for Low Power Motion Estimation VLSI Architectures", in Proc. IEEE Workshop Signal Process. Syst. (SiPS), Oct. 2000, pp. 149–158.

- [8] In Suk Chong and Antonio Ortega, "Dynamic Voltage Scaling Algorithms for Power Constrained Motion Estimation", in Proc.

- IEEE Int. Conf. Acoust., Speech, Signal Process. (ICASSP), vol. 2. Apr. 2007, pp. II-101–II-104.

- [9] Antonio Ortega and In Suk Chong, "Power Efficient Motion Estimation using Multiple Imprecise Metric Computations", in Proc. IEEE Int. Conf. Multimedia Expo, Jul. 2007, pp. 2046–2049

- [10] Debabrata Mohapatra, Georgios Karakonstantis and Kaushik Roy, "Significance Driven Computation: A Voltage-Scalable, Variation-Aware and Quality- Tuning Motion Estimator", in Proc. 14th ACM/IEEE Int. Symp. Low Power Electron. Design (ISLPED), 2009, pp. 195–200.

- [11] J. George, B. Marr, B. E. S. Akgul, and K. V. Palem, "Probabilistic Arithmetic and Energy Efficient Embedded Signal Processing", in Proc.Int. Conf. Compil., Archit., Synth. Embedded Syst. (CASES), 2006, pp. 158–168.